Description

Introduction

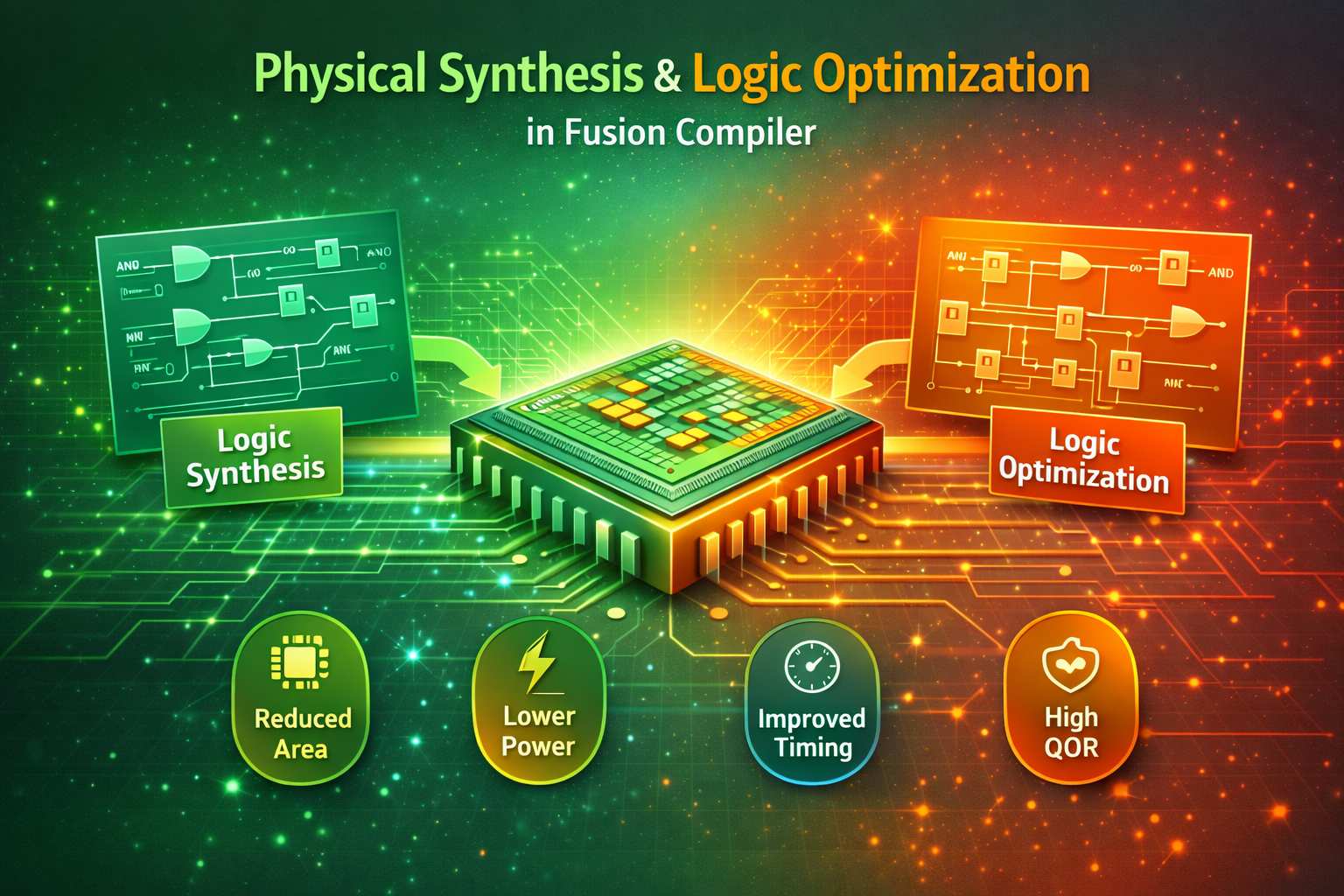

Physical Synthesis & Logic Optimization in Synopsys Fusion Compiler focuses on transforming RTL into an optimized gate-level design. It considers physical factors such as placement, timing, power, and congestion. As a result, designers achieve better accuracy early in the flow.

Moreover, this training explains synthesis techniques that are tightly integrated with physical design. Therefore, learners can improve QoR (Quality of Results) and achieve faster convergence. In addition, the course helps in efficient timing closure for advanced semiconductor nodes.

Learner Prerequisites

- Basic understanding of digital electronics and CMOS concepts

- Familiarity with RTL design using Verilog/SystemVerilog

- Knowledge of synthesis and static timing analysis (STA) fundamentals

- Understanding of physical design concepts such as placement and routing

- Exposure to Linux/Unix environments and basic scripting (Tcl preferred)

Table of Contents

1. Physical Synthesis Fundamentals

1.1 Overview of Physical Synthesis in Fusion Compiler

1.2 Differences Between Logical and Physical Synthesis

1.3 Unified RTL-to-GDSII Flow Concepts

1.4 Understanding QoR Metrics (Timing, Area, Power)

1.5 Design Initialization for Physical Synthesis

1.6 Technology Libraries and Timing Models

1.7 Physical Constraints and Floorplan Awareness

1.8 Introduction to MCMM (Multi-Corner Multi-Mode)

2. Design Setup for Logic Optimization

2.1 Importing RTL and Design Elaboration

2.2 Linking Technology Libraries and Constraints

2.3 Defining Clock Constraints and Timing Intent

2.4 Setting Design Environment (Operating Conditions)

2.5 Handling Hierarchical vs Flat Designs

2.6 Design Rule Constraints (DRC) Setup

2.7 Path Grouping and Timing Exceptions

2.8 Constraint Validation and Debugging

3. Synthesis Optimization Techniques

3.1 Compile Strategies and Optimization Modes

3.2 Timing-Driven Synthesis Optimization

3.3 Area and Power Optimization Techniques

3.4 Multi-Vt Cell Optimization

3.5 Resource Sharing and Logic Restructuring

3.6 Register Optimization and Retiming

3.7 Handling High Fanout and Critical Paths

3.8 Incremental and ECO Synthesis

4. Physical-Aware Logic Optimization

4.1 Placement-Aware Optimization Techniques

4.2 Congestion-Driven Synthesis Optimization

4.3 Wireload vs Physical Estimation Models

4.4 Physical Guidance in Optimization

4.5 Optimization Across Placement Boundaries

4.6 Buffering and Gate Sizing with Physical Awareness

4.7 Impact of Floorplan on Logic Optimization

4.8 Cross-Probing Between Logical and Physical Domains

5. Timing Optimization and Closure Techniques

5.1 Setup and Hold Time Optimization

5.2 Clock Path Optimization and CTS Awareness

5.3 Path-Based vs Graph-Based Optimization

5.4 Advanced Timing Analysis Techniques

5.5 Fixing Violations (Setup, Hold, Transition, Capacitance)

5.6 Useful Skew and Timing Borrowing

5.7 Multi-Scenario Timing Optimization

5.8 Timing ECO Strategies

6. Power Optimization Strategies

6.1 Dynamic and Leakage Power Reduction Techniques

6.2 Clock Gating Optimization

6.3 Multi-Bit Register Optimization

6.4 Power-Driven Synthesis Techniques

6.5 Voltage Domain and Power Intent (UPF Basics)

6.6 Activity-Based Optimization

6.7 Trade-offs Between Power, Timing, and Area

6.8 Low Power Design Best Practices

7. Advanced Optimization Features in Fusion Compiler

7.1 Machine Learning-Based Optimization Features

7.2 Fusion Compiler Optimization Engines Overview

7.3 Concurrent Optimization Across Metrics

7.4 Adaptive Optimization Strategies

7.5 Scenario Reduction Techniques

7.6 Handling Advanced Technology Nodes (7nm, 5nm, and below)

7.7 Variation-Aware Optimization

7.8 Reliability and Signal Integrity Considerations

8. Analysis, Reporting, and Debugging

8.1 Timing, Area, and Power Reporting

8.2 QoR Analysis and Comparison Techniques

8.3 Debugging Timing Violations

8.4 Identifying Optimization Bottlenecks

8.5 Visualization Tools for Analysis

8.6 Design Rule Checking and Fixing Violations

8.7 Cross-Tool Verification and Correlation

8.8 Best Practices for Debugging

9. ECO and Incremental Optimization Flow

9.1 Engineering Change Order (ECO) Concepts

9.2 Incremental Compilation and Optimization

9.3 Timing ECO Fixes Post-Placement

9.4 Functional ECO vs Timing ECO

9.5 Minimizing Design Impact During ECO

9.6 Verification After ECO Changes

9.7 Automation of ECO Flows

9.8 Signoff Considerations

10. Best Practices and Industry Use Cases

10.1 Best Practices for Physical Synthesis

10.2 Optimization Strategies for High-Performance Designs

10.3 Low-Power Design Case Studies

10.4 Handling Large-Scale SoC Designs

10.5 Common Challenges and Solutions

10.6 Design Convergence Techniques

10.7 Tool Configuration Best Practices

10.8 Real-World Implementation Scenarios

Conclusion

This training provides a complete understanding of physical synthesis and logic optimization using Fusion Compiler. It helps learners improve design convergence and achieve better QoR.

Furthermore, participants gain practical knowledge to handle timing closure challenges effectively. As a result, they can work confidently on complex chip designs across advanced technology nodes.

Reviews

There are no reviews yet.