Description

Introduction

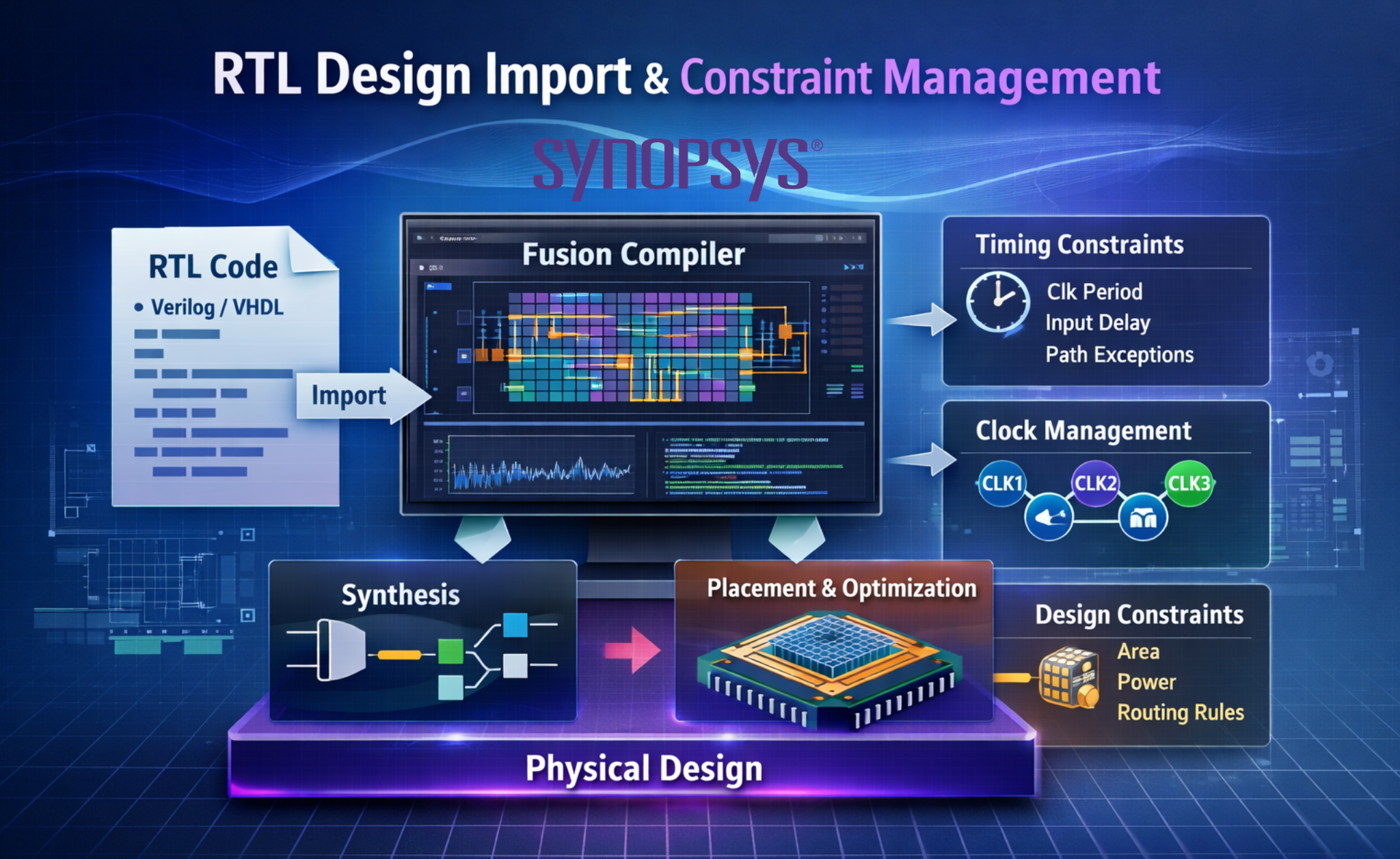

RTL Design Import & Constraint Management in Synopsys Fusion Compiler focuses on the early stages of physical design. In this phase, RTL is imported into the implementation environment. At the same time, constraints are defined to guide synthesis, placement, and optimization.

This training provides a structured approach to design initialization. Moreover, it explains constraint creation and timing intent in detail. As a result, learners can build a robust and convergent design flow.

Learner Prerequisites

- Basic understanding of digital design and RTL concepts such as Verilog or VHDL

- Familiarity with synthesis and static timing analysis fundamentals

- Knowledge of the semiconductor design flow from front-end to back-end

- Basic exposure to EDA tools and Linux environments

- Understanding of timing constraints and clocking concepts

Table of Contents

1. RTL Design Import Fundamentals

1.1 Overview of Fusion Compiler design flow

1.2 Understanding RTL handoff and design inputs

1.3 Supported RTL formats and coding guidelines

1.4 Importing RTL into the Fusion Compiler environment

1.5 Handling hierarchical versus flat designs

1.6 Design elaboration and initial checks

1.7 Debugging RTL import issues

1.8 Managing multi-file and multi-language designs

2. Library and Technology Setup

2.1 Technology file and library overview

2.2 Logical versus physical libraries

2.3 Milkyway/NDM library setup

2.4 Linking standard cell and memory libraries

2.5 Handling multi-voltage and multi-Vt libraries

2.6 Library consistency checks

2.7 Corner and variation setup

2.8 Best practices for library management

3. Design Initialization and Environment Setup

3.1 Creating design environments and workspaces

3.2 Setting up design variables and paths

3.3 Floorplan awareness during the import stage

3.4 Initial design checks and validation

3.5 Managing design hierarchy and modules

3.6 Handling black boxes and IP integration

3.7 Importing UPF/CPF for power intent

3.8 Version control and design data management

4. Constraint Management Fundamentals

4.1 Importance of constraints in physical design

4.2 Types of constraints in Fusion Compiler

4.3 Overview of Synopsys Design Constraints (SDC)

4.4 Constraint flow across design stages

4.5 Constraint validation and debugging

4.6 Common constraint issues and fixes

4.7 Best practices for constraint definition

4.8 Constraint reuse across projects

5. Clock Definition and Management

5.1 Creating primary clocks

5.2 Generated and derived clocks

5.3 Clock latency and uncertainty

5.4 Clock groups and relationships

5.5 Handling multiple clock domains

5.6 Asynchronous and synchronous clocks

5.7 Clock gating constraints

5.8 Debugging clock definition issues

6. Timing Constraints and Exceptions

6.1 Input and output delay constraints

6.2 Setup and hold timing constraints

6.3 False paths and multicycle paths

6.4 Maximum and minimum delay constraints

6.5 Case analysis and conditional constraints

6.6 Path-based versus graph-based analysis

6.7 Timing exception best practices

6.8 Debugging timing violations

7. Physical and Design Constraints

7.1 Area and utilization constraints

7.2 Placement constraints and regions

7.3 Blockages and keep-out margins

7.4 Routing constraints overview

7.5 Pin placement constraints

7.6 Congestion-aware constraints

7.7 Power and ground constraints

7.8 DRC and LVS considerations

8. Multi-Corner Multi-Mode (MCMM) Setup

8.1 MCMM concepts and importance

8.2 Defining modes and corners

8.3 Scenario creation in Fusion Compiler

8.4 Constraint management across scenarios

8.5 Timing analysis in MCMM environments

8.6 Optimization challenges in MCMM

8.7 Debugging MCMM setup issues

8.8 Best practices for convergence

9. Constraint Validation and Debugging

9.1 Constraint consistency checks

9.2 Using reports for verification

9.3 Identifying missing or conflicting constraints

9.4 Debugging timing and functional issues

9.5 Constraint coverage analysis

9.6 Automation and scripting for validation

9.7 Common pitfalls in constraint definition

9.8 Signoff readiness checks

10. Automation and Scripting

10.1 TCL scripting basics for Fusion Compiler

10.2 Automating RTL import flows

10.3 Script-based constraint creation

10.4 Batch versus interactive mode

10.5 Reusable scripts and templates

10.6 Debugging scripts and logs

10.7 Integration with CI/CD flows

10.8 Best practices for automation

11. Integration with Synthesis and Physical Design

11.1 Constraint handoff to synthesis

11.2 Consistency between RTL and netlist constraints

11.3 Interaction with placement and optimization

11.4 Early timing analysis and feedback loops

11.5 Cross-stage constraint alignment

11.6 Handling ECOs and design changes

11.7 Incremental constraint updates

11.8 Best practices for smooth integration

12. Advanced Topics in Constraint Management

12.1 Power-aware constraints

12.2 Low-power design using UPF/CPF

12.3 Handling complex SoC designs

12.4 Constraint partitioning for large designs

12.5 Hierarchical constraint management

12.6 Machine learning in constraint optimization

12.7 Advanced debugging techniques

12.8 Industry case studies

Conclusion

This training builds a strong foundation in RTL import and constraint management. It also helps learners define accurate timing intent. Furthermore, it ensures a smooth transition into physical design stages. As a result, designers can achieve faster convergence and better design quality.

Reviews

There are no reviews yet.