Description

Introduction:

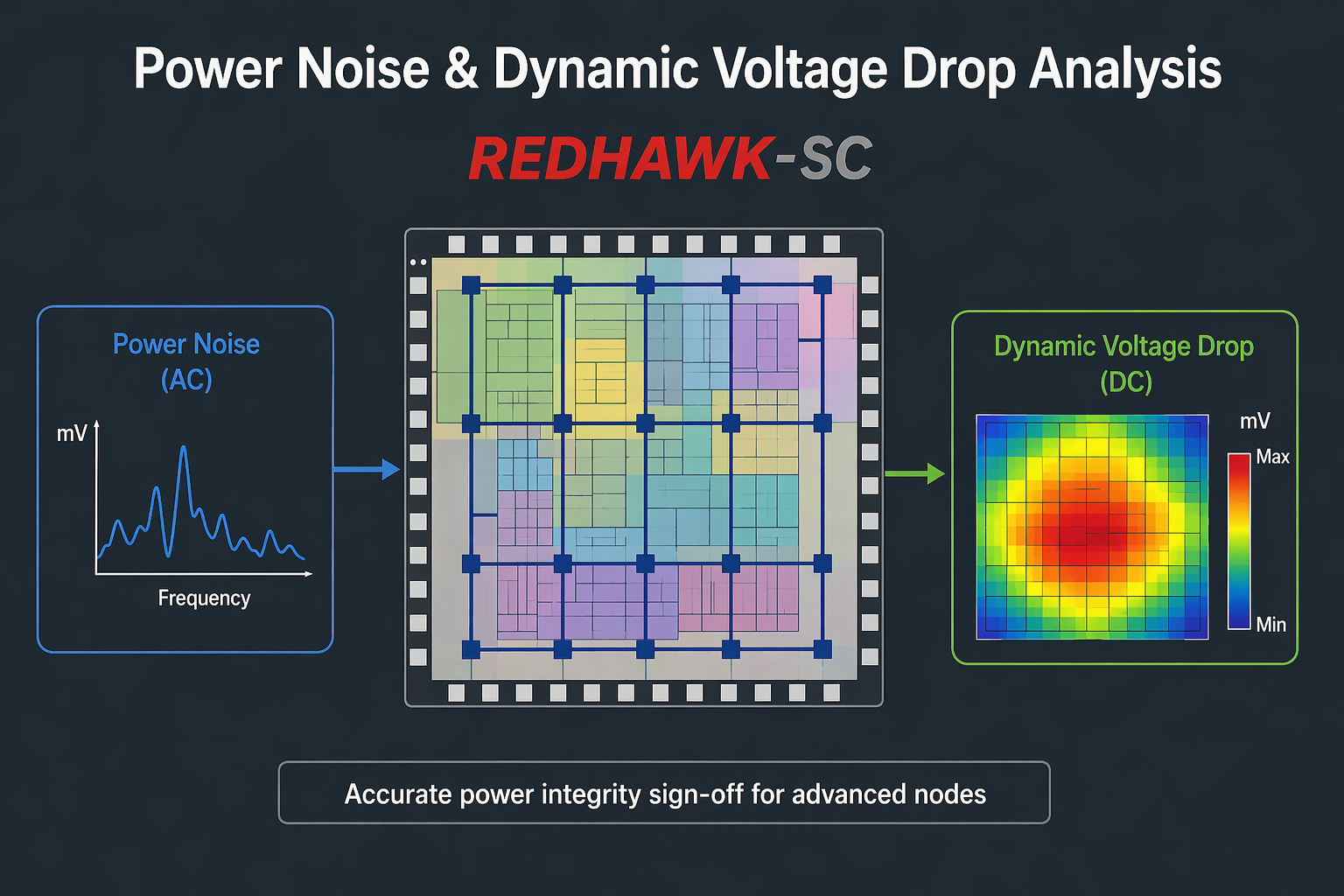

Synopsys RedHawk-SC is an advanced power integrity signoff platform. It is used for analyzing IR drop, electromigration (EM), and power noise in high-performance SoC designs. Moreover, it enables accurate static and dynamic voltage drop analysis and switching noise detection. Therefore, it ensures reliable power grid validation for silicon signoff.

Learner Prerequisites:

- Basic understanding of CMOS VLSI design and power distribution networks (PDN)

- Familiarity with STA, timing, and signoff concepts

- Knowledge of IR drop, EM, and switching activity fundamentals

- Exposure to UPF/CPF power intent methodologies

- Basic experience with EDA flows and debugging concepts

Table of Contents

1. Introduction to Power Integrity in Advanced Nodes

1.1 Overview of power integrity challenges in nanometer technologies

1.2 Static vs dynamic voltage drop and their impact on silicon

1.3 Causes and sources of power noise in SoC designs

1.4 Importance of signoff-level power integrity analysis

1.5 Industry trends in low-power and high-performance design constraints

2. RedHawk-SC Architecture & Analysis Flow

2.1 Overview of RedHawk-SC platform and core engines

2.2 Power grid extraction and modeling methodology

2.3 Analysis flow from design import to signoff closure

2.4 Data inputs required for accurate analysis (netlist, libraries, activity)

2.5 Integration with physical design and signoff ecosystem

3. Design Data Setup for Power Noise Analysis

3.1 Import of netlist, LEF/DEF, and technology files

3.2 UPF/CPF power intent setup and domain definition

3.3 Switching activity generation using VCD/SAIF files

3.4 Library characterization and corner setup

3.5 Verification of design readiness for power analysis

4. Dynamic Voltage Drop (DVD) Analysis Methodology

4.1 Time-based and event-driven voltage drop simulation

4.2 Switching current modeling and peak activity estimation

4.3 Identification of worst-case voltage drop windows

4.4 Vector-based vs vectorless analysis approaches

4.5 Correlation of dynamic drop with timing and performance

5. Power Noise Analysis & Decoupling Strategy

5.1 Simultaneous switching noise (SSN) mechanisms

5.2 On-chip decoupling capacitor modeling and placement

5.3 Power grid resistance and inductance effects on noise

5.4 Noise hotspot detection and root cause analysis

5.5 Noise mitigation techniques and design fixes

6. Advanced Analysis Techniques in RedHawk-SC

6.1 Hierarchical analysis for large-scale SoC designs

6.2 Multi-corner, multi-mode (MCMM) power analysis

6.3 Temperature and process variation impact on noise

6.4 Vectorless estimation and early-stage analysis flow

6.5 Correlation between pre-layout and post-layout results

7. Debugging & Visualization of Voltage Drop Results

7.1 Hotspot identification and classification techniques

7.2 Waveform-based debugging of power events

7.3 Grid viewer analysis and layer-wise investigation

7.4 Reporting and result interpretation for engineers

7.5 Correlation with silicon debug and measurement data

8. Signoff Closure & Optimization Strategies

8.1 Power integrity signoff requirements and criteria

8.2 Iterative fix-and-verify design optimization flow

8.3 Tradeoff analysis between power, performance, and area

8.4 Final signoff checklist and quality metrics

8.5 Best practices for robust power integrity closure

Conclusion:

This training provides a complete and structured understanding of power noise and dynamic voltage drop analysis using RedHawk-SC. In addition, it enables effective debugging and optimization of power integrity issues. Therefore, it ensures robust signoff and reliable SoC design closure.

Reviews

There are no reviews yet.