Description

Introduction

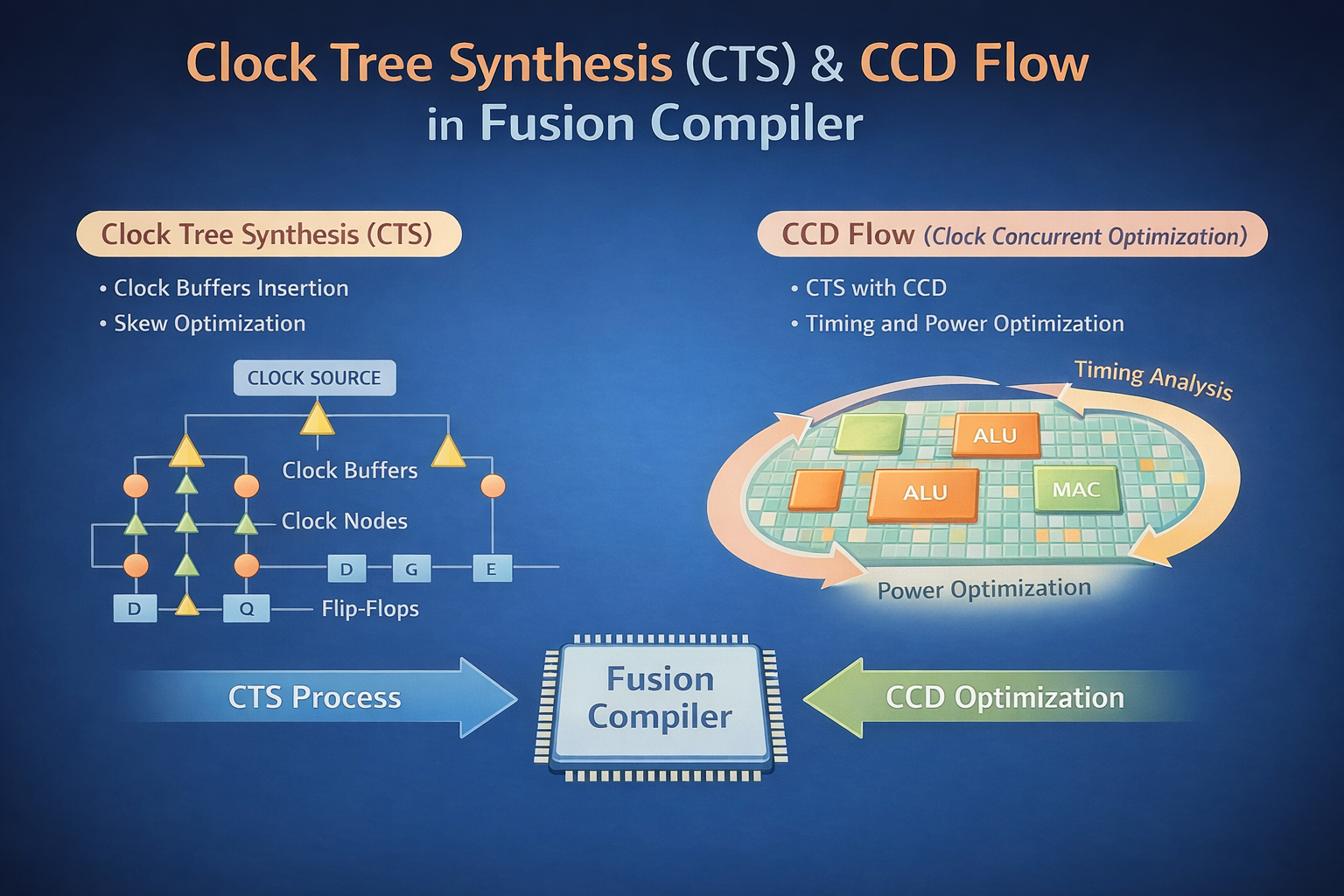

Clock Tree Synthesis (CTS) & CCD Flow in Synopsys Fusion Compiler focuses on building a balanced and optimized clock network while ensuring timing, power, and skew requirements are met. CTS is a critical stage in physical design because it directly impacts performance, reliability, and overall timing closure. In addition, the CCD (Clock Concurrent Optimization / Clock Concurrent Design flow in Fusion Compiler) enables simultaneous optimization of clock and data paths for better QoR and faster convergence.

This training provides a deep understanding of clock architecture design, insertion strategies, skew management, and advanced optimization techniques used in modern semiconductor designs.

Learner Prerequisites

Basic understanding of digital design and CMOS fundamentals

Knowledge of RTL design and synthesis flow

Understanding of static timing analysis (STA) concepts

Familiarity with physical design stages (placement, routing basics)

Basic exposure to clock concepts such as skew, latency, and jitter

Linux/Unix environment and Tcl scripting basics

Table of Contents

1. Clock Tree Synthesis Fundamentals

1.1 Overview of CTS in Fusion Compiler

1.2 Importance of Clock Networks in VLSI Design

1.3 Clock Distribution Challenges

1.4 Clock Tree vs Clock Mesh Architecture

1.5 Clock Latency, Skew, and Jitter Concepts

1.6 CTS Design Goals and Metrics

1.7 Role of Buffer Insertion in CTS

1.8 Clock Domain Basics and Clock Groups

2. Clock Design Setup and Constraints

2.1 Defining Clock Sources and Clock Definitions

2.2 Clock Uncertainty and Latency Modeling

2.3 Timing Constraints for Clock Networks

2.4 False Path and Multicycle Path Handling

2.5 Clock Grouping and Isolation Techniques

2.6 Handling Generated and Gated Clocks

2.7 Constraint Validation and Debugging

2.8 Integration with MCMM Analysis

3. CTS Flow in Fusion Compiler

3.1 Pre-CTS Placement Considerations

3.2 Clock Tree Specification (CTS Spec File)

3.3 Clock Tree Building Process

3.4 Buffer/Invert Tree Construction

3.5 Clock Sink Clustering Techniques

3.6 Clock Routing Strategies

3.7 Post-CTS Optimization Steps

3.8 CTS Quality Checks and Signoff Metrics

4. Clock Concurrent Design (CCD) Flow

4.1 Introduction to CCD Concept

4.2 Differences Between CTS and CCD Flow

4.3 Concurrent Optimization of Data and Clock Paths

4.4 Timing-Driven Clock Optimization

4.5 Early Clock Planning in Placement Stage

4.6 Interaction Between CTS and Optimization Engines

4.7 Benefits of CCD in Advanced Nodes

4.8 Design Convergence Improvements with CCD

5. Clock Skew and Latency Optimization

5.1 Types of Clock Skew (Local vs Global)

5.2 Useful Skew Techniques

5.3 Skew Balancing Strategies

5.4 Latency Reduction Techniques

5.5 Clock Tree Buffer Optimization

5.6 Impact of Routing on Skew

5.7 Skew Constraints in Multi-Mode Designs

5.8 Debugging Skew Violations

6. Power Optimization in Clock Networks

6.1 Clock Gating Techniques

6.2 Integrated Clock Gating (ICG) Cells

6.3 Reducing Clock Switching Activity

6.4 Multi-Bit Clock Optimization

6.5 Power-Aware CTS Strategies

6.6 Trade-offs Between Power and Skew

6.7 Leakage Reduction in Clock Buffers

6.8 Power Intent (UPF) Impact on CTS

7. Advanced CTS Techniques in Fusion Compiler

7.1 Machine Learning-Based Clock Optimization

7.2 Variation-Aware Clock Tree Design

7.3 On-Chip Variation (OCV) Handling

7.4 Advanced Buffer Insertion Strategies

7.5 Clock Tree Rebalancing Techniques

7.6 Signal Integrity Considerations

7.7 High-Frequency Clock Network Design

7.8 Multi-Clock Domain Optimization

8. CTS Debugging and Analysis

8.1 CTS Report Analysis (Skew, Latency, QoR)

8.2 Identifying Clock Tree Bottlenecks

8.3 Debugging Hold and Setup Violations

8.4 Cross-Probing Clock and Data Paths

8.5 Visualization of Clock Networks

8.6 Impact Analysis of CTS Changes

8.7 DRC and Design Rule Checks for CTS

8.8 Best Practices for Debugging Clock Issues

9. Integration with Physical Design Flow

9.1 CTS Interaction with Placement Stage

9.2 Post-CTS Routing Considerations

9.3 Impact on Timing Closure Flow

9.4 ECO After CTS Implementation

9.5 Incremental CTS Optimization

9.6 Signoff Preparation After CTS

9.7 Coordination with Synthesis Results

9.8 Full Chip Integration Challenges

10. Industry Best Practices and Case Studies

10.1 CTS Strategy for High-Performance Designs

10.2 Low-Power Clock Design Strategies

10.3 Handling Large SoC Clock Networks

10.4 Common CTS Failures and Fixes

10.5 Design Convergence Techniques

10.6 Real-World CCD Implementation Examples

10.7 Tool Optimization Guidelines

10.8 Best Practices for Stable Clock Networks

Conclusion

This training provides complete knowledge of CTS and CCD flow in Fusion Compiler. It helps learners design efficient, low-skew, and power-optimized clock networks.

Furthermore, it enables better understanding of concurrent optimization techniques. As a result, designers can achieve faster timing closure and improved QoR in advanced technology nodes.

Reviews

There are no reviews yet.