Description

Introduction

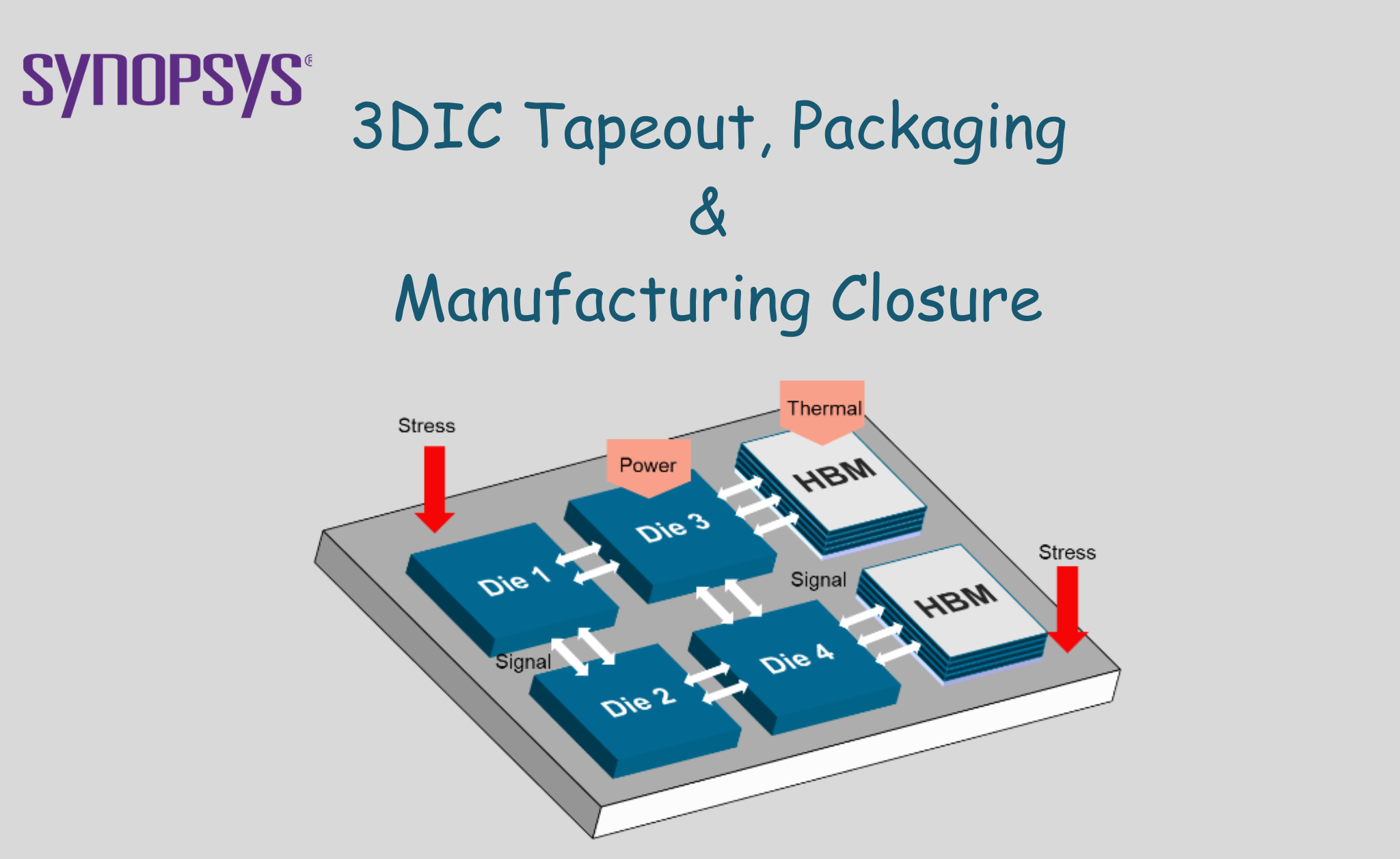

Synopsys 3DIC Compiler is an advanced platform for multi-die integration, verification, and physical signoff. It supports 3D IC design workflows including DRC, LVS, and hierarchical validation. Moreover, it enables early detection of design issues across stacked dies and interposers. In addition, it provides a unified environment for signoff-driven verification closure.

Learner Prerequisites

- Basic knowledge of VLSI physical design flow

- Understanding of DRC, LVS, and signoff concepts

- Familiarity with 2.5D/3D IC architectures such as TSV and chiplets

- Awareness of EDA verification tools and flows

- Basic understanding of design hierarchy and netlist concepts

Table of Contents

1 Introduction to Verification in Synopsys 3DIC Compiler

1.1 Overview of multi-die verification flow

1.2 Importance of signoff in 3D IC design

1.3 Challenges in heterogeneous integration verification

1.4 Role of physical and logical verification

1.5 Verification-driven design closure methodology

2 Verification Environment Setup for 3D ICs

2.1 Project setup and configuration flow

2.2 Multi-die hierarchy loading and management

2.3 Technology files and rule deck setup

2.4 Tool integration for verification flows

2.5 Pre-signoff readiness checks

3 Design Rule Check (DRC) Methodology

3.1 DRC fundamentals in multi-die environments

3.2 TSV, bump, and interposer rule validation

3.3 Advanced pattern and density rule checks

3.4 Die-to-die rule compliance verification

3.5 DRC debugging and violation fixing flow

4 Layout Versus Schematic (LVS) Verification Flow

4.1 Hierarchical LVS methodology in 3D ICs

4.2 Netlist vs layout comparison process

4.3 Cross-die connectivity validation techniques

4.4 Detection of opens, shorts, and mismatches

4.5 LVS debug and correction strategies

5 Multi-Die Connectivity and Integrity Checks

5.1 Chiplet-to-chiplet connectivity validation

5.2 Interposer routing correctness analysis

5.3 Signal continuity verification across dies

5.4 Hierarchical net integrity checks

5.5 Cross-domain design consistency validation

6 Power, Timing, and Physical Verification

6.1 Power integrity validation in stacked designs

6.2 Timing-aware verification considerations

6.3 IR drop and electromigration checks

6.4 Physical compliance validation strategies

6.5 Multi-domain consistency analysis

7 Advanced Debug and Verification Closure

7.1 Root cause analysis of verification failures

7.2 Iterative fix-and-reverify methodology

7.3 Automation in verification debugging

7.4 Hierarchical error tracing techniques

7.5 Convergence strategies for signoff closure

8 Multi-Die Signoff Methodology

8.1 Signoff criteria for 3D IC designs

8.2 Final DRC and LVS clean verification flow

8.3 Cross-die signoff validation strategy

8.4 Quality metrics for tape-out readiness

8.5 Final verification closure and release flow

Conclusion

This training provides a complete understanding of verification, DRC, LVS, and multi-die signoff using Synopsys 3DIC Compiler. Moreover, it explains how hierarchical verification is performed across complex 3D IC architectures. It also covers practical debugging methods for design rule violations and connectivity issues. Therefore, learners gain strong hands-on knowledge of signoff workflows and validation strategies. In addition, this foundation helps ensure robust, error-free, and tape-out ready multi-die designs.

Reviews

There are no reviews yet.